# SEGA SERVICE MANUAL

# GENESIS II /MEGA DRIVE II (PAL-B/I/G, RGB)

| <br>NO. | 001-1        |

|---------|--------------|

| ISSUED  | AUGUST, 1993 |

### SUPPLEMENT

The specifications of IC1 on page 16 are corrected as follows.

Sega Enterprises, Ltd.

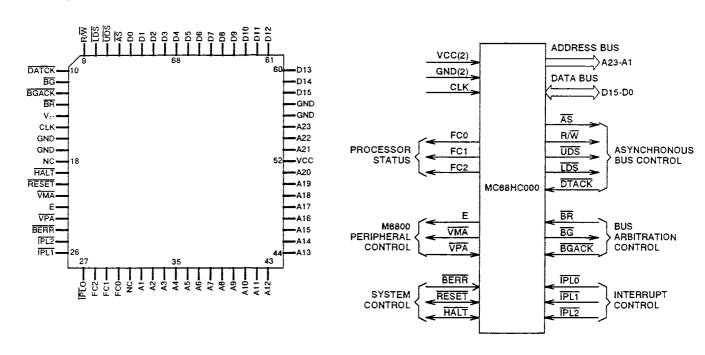

#### IC1 16/32-Bit Microprocessor

IC MC68HC000FN8

IC HD68HC000CP8

■ Top View & Pin Layout

■ Signal Description

#### Description

| No. | Pin Name        | 1/0 | Function              | No | Pin Name                | I/O | Function                 |            | lo. | Pin Name                    | I/O | Function     |

|-----|-----------------|-----|-----------------------|----|-------------------------|-----|--------------------------|------------|-----|-----------------------------|-----|--------------|

| 1   | $D_4$           |     |                       | 23 | VPA                     | I   | Vaild Peripheral Address |            | 46  | A <sub>15</sub>             |     |              |

| 2   | $D_3$           |     |                       | 24 | BERR                    | I   | Bus Error                | 1 4        | 47  | A <sub>16</sub>             |     |              |

| 3   | <del></del>     | I/O | Data Bus              | 25 | IPL <sub>2</sub>        |     |                          | 1 4        | 48  | A <sub>17</sub>             | 0   | Address Bus  |

| 4   | D <sub>1</sub>  |     |                       | 26 | IPL <sub>1</sub>        | I   | Interrupt Control        | 4          | 19  | A <sub>18</sub>             |     | Addiess Das  |

| 5   | $D_0$           |     |                       | 27 | <u>IPL</u> <sub>o</sub> |     |                          | 5          | 50  | A <sub>19</sub>             |     |              |

| 6   | ĀS              | 0   | Address Strobe        | 28 | $FC_2$                  |     |                          | 5          | 51  | A <sub>20</sub>             |     |              |

| 7   | ÜDS             | 0   | Upper Data Strobe     | 29 | FC <sub>1</sub>         | 0   | Processor Status         |            | 52  | $V_{CC}$                    | _   | Power Supply |

| 8   | LDS             | Ο   | Lower Data Strobe     | 30 | FC <sub>0</sub>         |     |                          | 5          | 53  | A <sub>21</sub>             |     |              |

| 9   | R/W             | 0   | Read/Write            | 31 | N.C                     | -   |                          | 5          | 54  | A <sub>22</sub>             | Ο   | Address Bus  |

| 10  | DTACK           | T   | Data Transfer         | 32 | A <sub>1</sub>          |     |                          | 5          | 55  | A <sub>23</sub>             |     |              |

| 10  | DIACK           | 1   | Acknowledge           | 33 | A <sub>2</sub>          |     |                          | 5          | 56  | V <sub>SS</sub>             | _   | GND          |

| 11  | BG              | О   | Bus Grant             | 34 | A <sub>3</sub>          |     |                          | 5          | 57  | V <sub>SS</sub>             |     | עאט          |

| 12  | BGACK           | I   | Bus Grant Acknowledge | 35 | A <sub>4</sub>          |     |                          | 5          | 58  | D <sub>15</sub>             |     | 1            |

| 13  | BR              | I   | Bus Request           | 36 | A <sub>5</sub>          |     |                          | 5          | 59  | D <sub>14</sub>             |     |              |

| 14  | $V_{CC}$        |     | Power Supply          | 37 | A <sub>6</sub>          |     |                          | 6          | 50  | D <sub>13</sub>             |     |              |

| 15  | CLK             | I   | Clock                 | 38 | A <sub>7</sub>          | 0   | Address Bus              | 6          | 51  | $D_{12}$                    |     |              |

| 16  | V <sub>SS</sub> |     | GND                   | 39 | A <sub>8</sub>          | U   | Addless Dus              | $\epsilon$ | 52  | $D_{11}$                    |     |              |

| 17  | V <sub>SS</sub> |     | UND                   | 40 | A <sub>9</sub>          |     |                          | 6          | 53  | $D_{10}$                    | I/O | Data Bus     |

| 18  | NC              | _   | Not Connected         |    |                         | 6   | 54                       | $D_9$      | İ   |                             |     |              |

| 19  | HALT            | I/O | Halt                  | 42 | A <sub>11</sub>         |     |                          | $\epsilon$ | 55  | $D_8$                       |     |              |

| 20  | RES             | I/O | Reset                 | 43 | A <sub>12</sub>         |     |                          | 1          | 56  | $\overline{\mathrm{D}_{7}}$ |     |              |

| 21  | VMA             | 0   | Vaild Memory Address  | 44 | A <sub>13</sub>         |     |                          | 1          | 57  | $D_6$                       |     |              |

| 22  | Е               | 0   | Enable                | 45 | A <sub>14</sub>         |     |                          | 1          | 58  | $D_5$                       |     |              |

## Differences between MEGA DRIVE and MEGA DRIVE 2

#### • Electrical Components

Note: For components marked (\*\*), components equivalent to those listed and made by other companies can also be used.

| Component                       | MEGA DRIVE                    | MEGA DRIVE 2          | Remarks                           |  |  |

|---------------------------------|-------------------------------|-----------------------|-----------------------------------|--|--|

| MAIN CPU                        | MC68000 DIP (*X)              | HC68HC000FN8 PLCC (%) | Package changed.                  |  |  |

| SUB CPU                         | Z80A DIP                      | Z84C0006 QFP (**)     | Package changed.                  |  |  |

| VIDEO DISPLAY PROCESSOR         | CUSTOM CHIP YM7101            |                       |                                   |  |  |

| BUS ARBITER                     | CUSTOM CHIP<br>UPD92271GD-001 | CUSTOM CHIP FC1001    | Integrated into one chip.         |  |  |

| FM SOUND SOURCE                 | YM2612                        |                       |                                   |  |  |

| RGB ENCODER                     | MB3514                        | Same as on left       |                                   |  |  |

| REGULATOR IC                    | MA7805UC (※)                  | UPC7805HF (※)         |                                   |  |  |

| OP AMP                          | LM358 DIP                     | LM224 SOD (W)         |                                   |  |  |

| HEADPHONE AMP                   | CXA1034P                      | LM324 SOP (※)         | Integrated with op amp.           |  |  |

| MEMORY FOR MAIN CPU             | TC51382-12 DIP (**)           | TC51832AFL-10 SOP (*) | Package changed.                  |  |  |

| MEMORY FOR SUB CPU              | KM6264BL-12 DIP600 (*)        | KM6264BLG-10 SOP (※)  | Package changed.                  |  |  |

| MEMORY FOR VDP                  | UPD41264V-12 (※)              | Same as on left       |                                   |  |  |

| OSCILLATOR                      | OSC 53. 203424M20PPM (*)      | Same as on left       |                                   |  |  |

| SUB BOARD FOR DC JACK           | Yes                           | No                    | Integrated into main board.       |  |  |

| SUB BOARD FOR<br>HEADPHONE JACK | Yes                           | No                    | As the headphone jack is omitted. |  |  |

### Features

| Item             | MEGA DRIVE         | MEGA DRIVE 2                   | Remarks                                     |

|------------------|--------------------|--------------------------------|---------------------------------------------|

| HEADPHONE JACK   | Yes                | No                             |                                             |

| HEADPHONE VOLUME | Yes                | No                             |                                             |

| RF OUT/CH SWITCH | Yes                | No                             | Integrated with RF unit.                    |

| POWER SWITCH     | Slide switch       | Push-button                    |                                             |

| DC JACK          | Pin plug for DC/NP | CONN DC JACK<br>EIAJ 3 HEC3100 | Changed as the AC adapter has been changed. |

| RESET SWITCH     | Tact push button   | Same as on left                |                                             |

| AC ADAPTER       | 1.2 A              | 0.85 A                         | Same as for MASTER<br>SYSTEM II.            |

## **Differences between GENESIS and GENESIS 2**

#### Electrical Components

Note: For components marked (%), components equivalent to those listed and made by other companies can also be used.

| Component                       | GENESIS                 | GENESIS 2            | Remarks                           |

|---------------------------------|-------------------------|----------------------|-----------------------------------|

| MAIN CPU                        | MC68HC000FN8 (%)        | Same as on left (**) |                                   |

| SUB CPU                         | Z80A DIP                | Z84C0006 QFP         | Package changed.                  |

| VIDEO DISPLAY PROCESSOR         |                         |                      |                                   |

| BUS ARBITER                     | CUSTOM CHIP FC1004      | Same as on left      | Integrated into one chip.         |

| FM SOUND SOURCE                 |                         |                      |                                   |

| RGB ENCODER                     | CXA1145M-16             | Same as on left      |                                   |

| REGULATOR IC                    | UPC7805HF               | Same as on left      |                                   |

| OP AMP                          | LM324                   | Same as on left      |                                   |

| HEADPHONE AMP                   | LM324                   | Same as on left      | Integrated with op amp.           |

| MEMORY FOR MAIN CPU             | TC51832FL-10 (%)        | Same as on left      |                                   |

| MEMORY FOR SUB CPU              | MB8464A-80 (※)          | Same as on left      |                                   |

| MEMORY FOR VDP                  | UPD41264V-12 (※)        | Same as on left      |                                   |

| OSCILLATOR                      | XTAL OSC 53. 693175 (*) | Same as on left      |                                   |

| SUB BOARD FOR<br>HEADPHONE JACK | Yes                     | No                   | As the headphone jack is omitted. |

#### Features

| Item             | GENESIS            | GENESIS 2                      | Remarks                                     |

|------------------|--------------------|--------------------------------|---------------------------------------------|

| HEADPHONE JACK   | Yes                | No                             |                                             |

| HEADPHONE VOLUME | Yes                | No                             |                                             |

| RF OUT/CH SWITCH | Yes                | No                             | Integrated with RF unit.                    |

| POWER SWITCH     | Slide switch       | Push-button                    |                                             |

| DC JACK          | Pin plug for DC/NP | CONN DC JACK<br>EIAJ 3 HEC3100 | Changed as the AC adapter has been changed. |

| RESET SWITCH     | Tact push button   | Same as on left                |                                             |

| AC ADAPTER       | 1.2 A              | 0.85 A                         | Same as for MASTER<br>SYSTEM II.            |

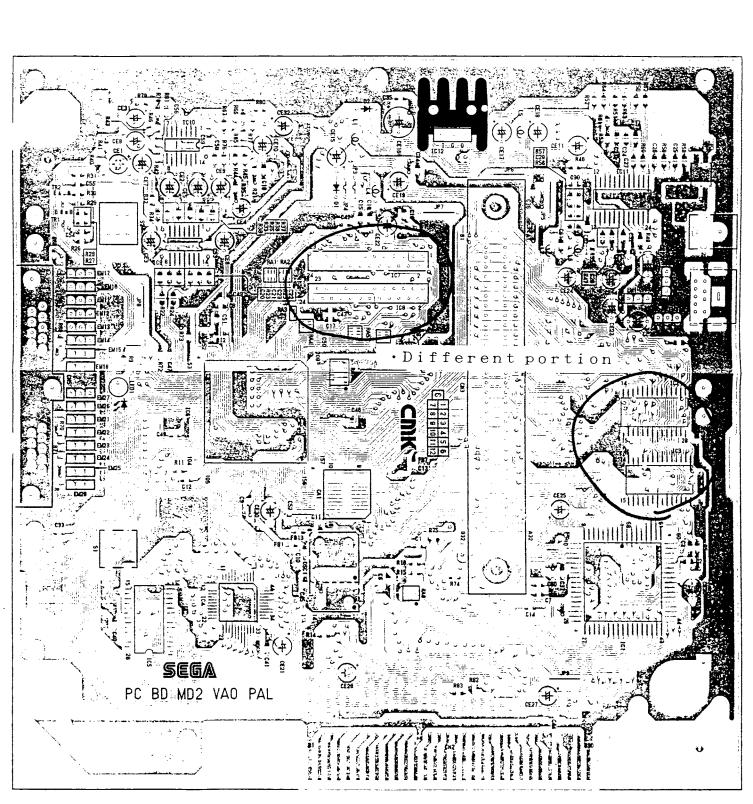

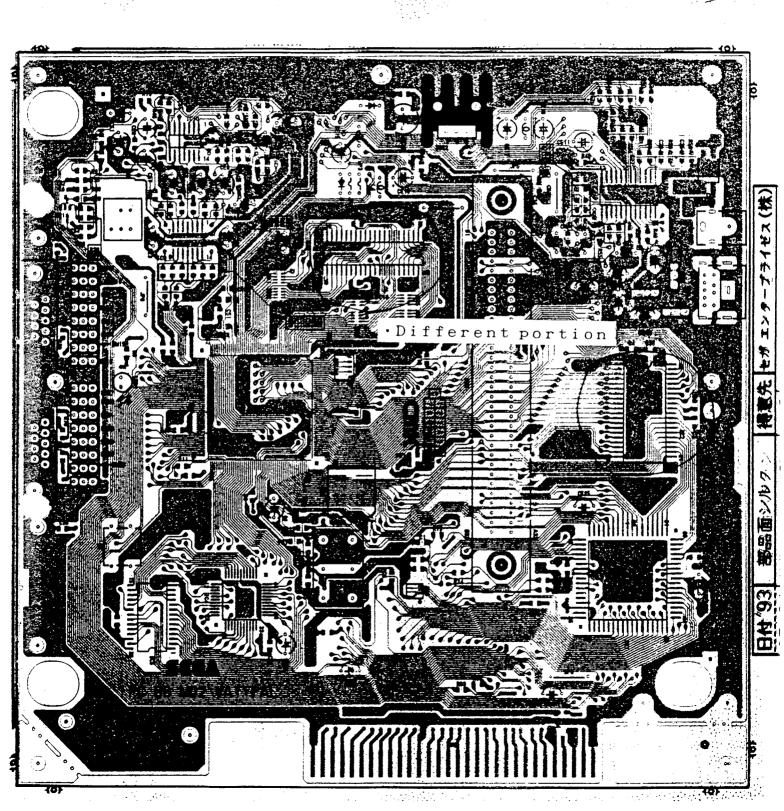

## DIFFERENCES BETWEEN Ver.O AND Ver.1 FOR MEGA DRIVE2/GENESIS2

1) Schematic Diagram

MEGA DRIVE 2/GENESIS 2 (Ver.0) MEGA DRIVE 2/GENES IS 2 (Ver.1) -(IC2)--(IC2&3)-UPD42832-15 -(IC7&8)--(IC7)-

2) Circuit Board Diagram

• See the attached.

RAMINTO

CUSTON PACK

UNCY

MEED PARTS NUMBERS

MEGA DRIVE 2/GENESIS 2 (Ver. 0)

w din

# MEGA DRIVE 2/GENESIS 2 (Ver. 1)

REVERSION POPPINER

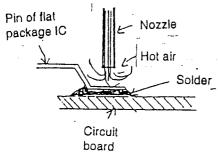

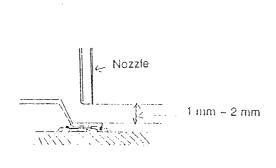

(1) Use a hot-air IC unsoldering machine to remove the flat package IC.

(2) Keep a space of approx. 1-2 mm between the IC remover's nozzle and flat package IC.

(3) After 20-30 seconds, the solder starts to melt; use tweezers to remove the IC.

\* The time required to melt the solder depends on the diameter of the nozzle.

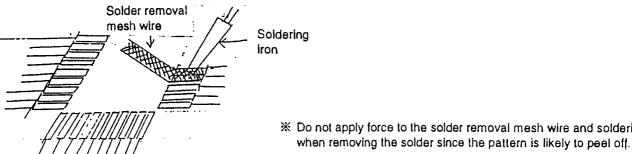

$\ensuremath{\mathbb{X}}$  Do not apply force to the solder removal mesh wire and soldering iron

#### Flat Package IC Installation

(1) Coat the circuit board from which the flat package IC has been removed with flux.

- (2) Place the good flat package IC to match the pattern on the board.

- (3) Temporarily fix the flat package IC at the four corners so it does not move.

(4) Solder all pins of the flat package IC.

Be careful not to short the pins since the spaces between the pins are very narrow.

- (5) After soldering, use thinner to rinse away the remaining flux.

- (6) Use a magnifying glass to check that there is no short-circuit.